Suppose we have to insert ‘1111’ inside the shift register.

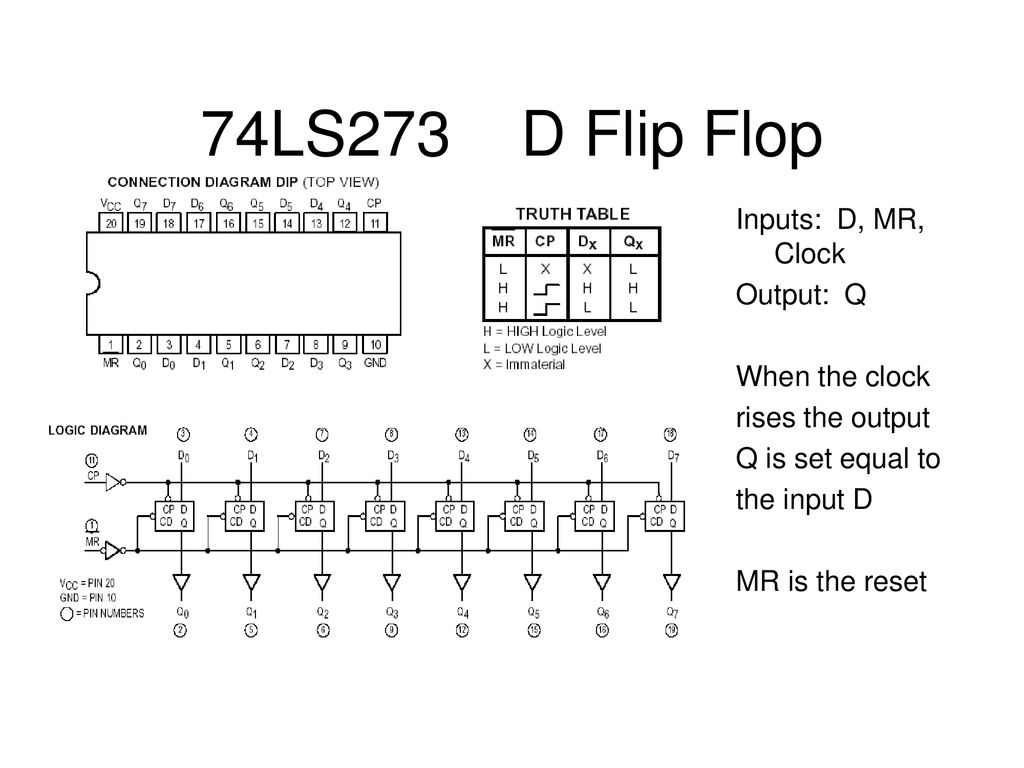

Let us now understand how data is stored in a shift register. Here we have assumed a shift right mode circuit as the data input is present at the left end while the stored bit is getting shifted towards the right so as to provide serial output. Thus the output of each flip-flop in the arrangement is logic low i.e., 0. Initially, we consider all the flip-flops are at reset mode. So consider a connection of 4 D flip-flops D 0 to D 3 as shown in the figure below: PIPO: Parallel-in Parallel-out: PIPO shift register permits both in and out of data bit in a parallel manner.Īs we have already discussed that a SISO is a type of shift register in which the input is fed serially and output is also taken in serial manner.PISO: Parallel-in Serial-out: This type of shift register allows the parallel input of data bit, but the output is taken serially.SIPO: Serial-in Parallel-out: Here the data is inserted serially either from the left or right direction.SISO: Serial-in Serial-out: It permits the insertion of data serially and taking the output also in a serial manner.So, the data bit movement inside the shift register give rise to various configurations which are as follows: It is to be noted here that data can be transferred in or out of the register either serially or parallely. The serial arrangement permits the output of one flip-flop to act as input to other and this allows the shifting of data bit inside the register. Shift registers are formed by the serial combination of D flip-flops, where each flip-flop in the arrangement holds single data bit.

Parallel to serial converter using mux and flipflops full#

0 kommentar(er)

0 kommentar(er)